Page 31 - 實現系統級效能、功耗與面積的3D-IC小晶片設計

P. 31

INNOVATIONS

visible) HBM加DDR的支援,以 及將HBM作為DDR支援快取記 憶體的軟體透明快取(software transparent caching)。」不 過,Sapphire Rapids首席工程 師Nevine Nassif先前接受《EE Times》訪問時表示,該HBM版本 得付出晶片面積的代價。

那些都沒有了──除了資料串流 (data-streaming)加速器──但 有HBM控制器。」Nassif補充指 出:「而且,為支援HBM的頻寬要 求,我們必須對網狀網路(mesh) 做一些改變。」

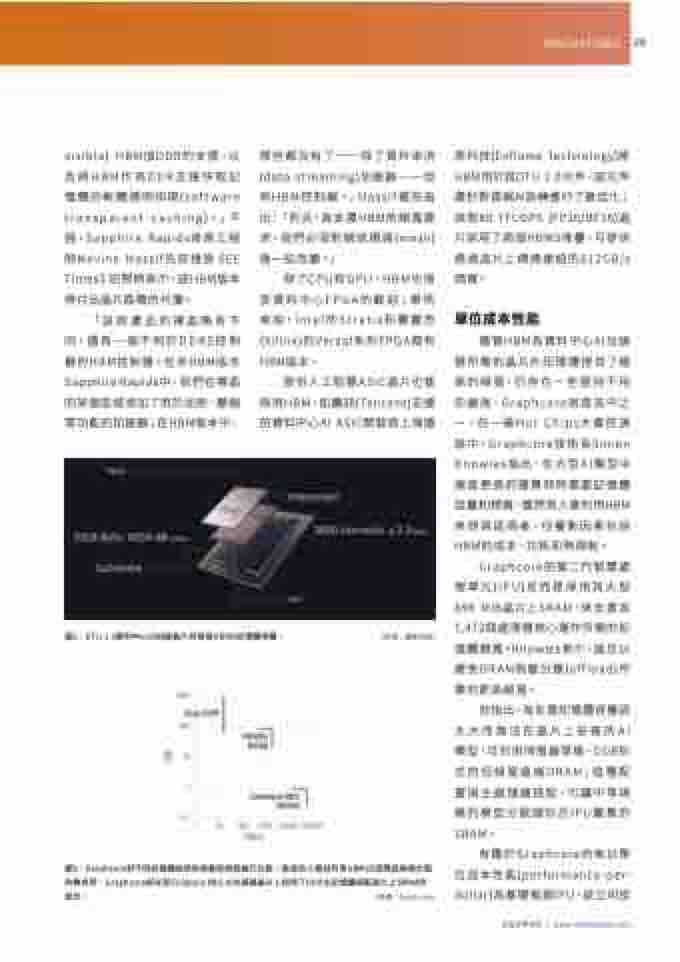

原科技(Enflame Technology)將 HBM用於其DTU 1.0元件,該元件 還針對雲端AI訓練進行了最佳化; 該款80 TFLOPS (FP16/BF16)晶 片採用了兩個HBM2堆疊,可提供 透過晶片上網路連結的512GB/s 頻 寬。

儘管HBM為資料中心AI加速 器所需的晶片外記憶體提供了極 高的頻寬,仍存在一些堅持不用 的廠商,Graphcore就是其中之 一。在一場Hot Chips大會的演 說中,Graphcore技術長Simon Knowles指出,在大型AI模型中 速度更高的運算同時需要記憶體 容量和頻寬,雖然有人會利用HBM 來提高這兩者,但權衡因素包括 HBM的成本、功耗和熱限制。

「該款產品的裸晶略有不 同,還有一個不同於DDR5控制 器的HBM控制器。在非HBM版本 Sapphire Rapids中,我們在裸晶 的某個區域添加了用於加密、壓縮 等功能的加速器;在HBM版本中,

除了CPU和GPU,HBM也很 受資料中心FPGA的歡迎;舉例 來說,Intel的Stratix和賽靈思 (Xilinx)的Versal系列FPGA都有 HBM版本。

單位成本性能

部份人工智慧ASIC晶片也會 採用HBM,如騰訊(Tencent)支援 的資料中心AI ASIC開發商上海燧

29

圖2:DTU 1.0資料中心AI加速晶片有兩個HBM2記憶體堆疊。

(來源:燧原科技)

Graphcore的第二代智慧處 理單元(IPU)反而是採用其大型 896 MiB晶片上SRAM,來支援其 1,472個處理器核心運作所需的記 憶體頻寬。Knowles表示,這足以 避免DRAM負載分擔(offload)所 需的更高頻寬。

圖3:Graphcore對不同記憶體技術的容量和頻寬進行比較。當其他人嘗試利用HBM2E因應這兩個方面 的需求時,Graphcore卻在其Colossus Mk2 AI加速器晶片上採用了DDR主記憶體搭配晶片上SRAM的 組合。 (來源:Graphcore)

有鑑於Graphcore向來以單 位成本性能(performance-per- dollar)為基礎推銷IPU,該公司拒

他指出,為支援記憶體容量因 太大而無法在晶片上安裝的AI 模型,可利用伺服器等級、DDR形 式的低頻寬遠端DRAM;這種配 置與主處理器搭配,可讓中等規 模的模型分散儲存於IPU叢集的 SRAM。

2022年4月 | www.eettaiwan.com