Synchronization in industrial 4.0 IEEE1588, redundancy and EtherCAT<sup>®</sup> *Presented by: Lichien Hu*

# Synchronization in industrial 4.0 IEEE1588, redundancy and EtherCAT<sup>®</sup>

#### Presented by: Lichien Hu Microchip Field Applications Engineer

### You May Hear the Following

# Why Synchronization?

"A man with a watch knows what time it is. A man with two watches is never sure."

— Segal's Law

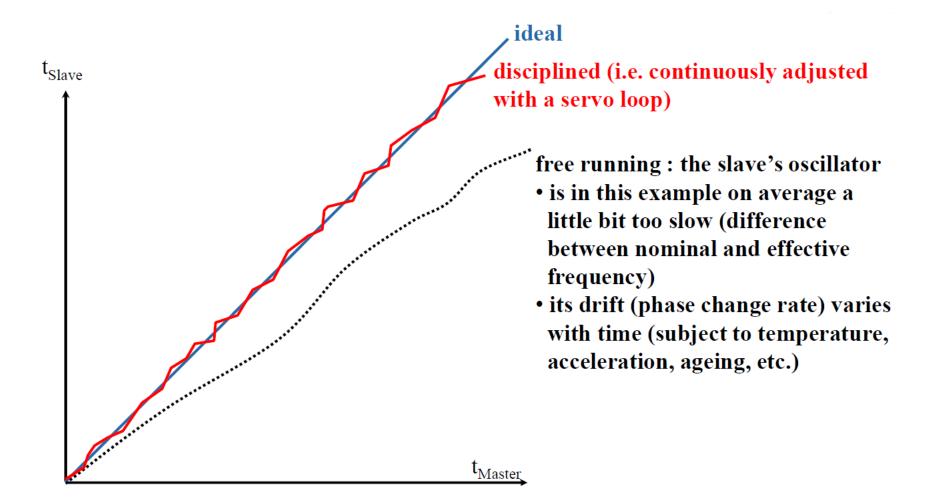

### Effect and Limitations of Clock Adjustment

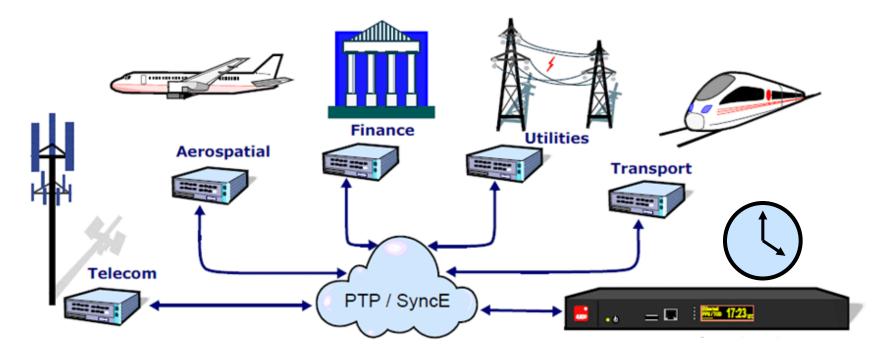

# Where is It Used (Applications)?

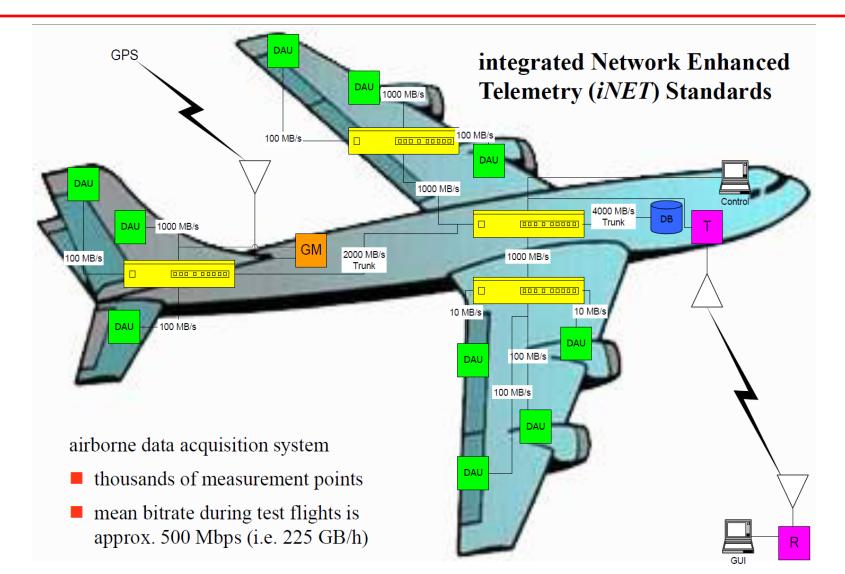

#### Distributed, real time control and data acquisition needed

## **Data Acquisition**

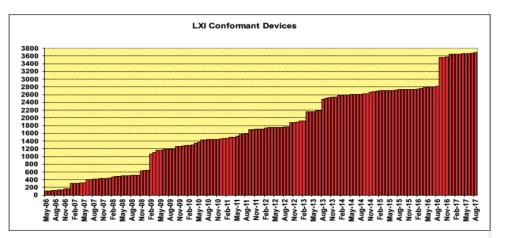

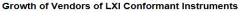

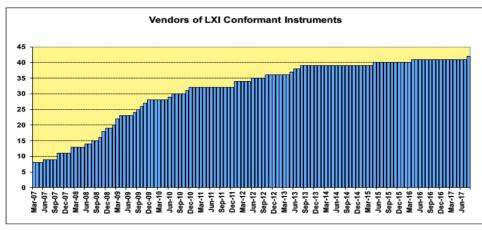

### LXI

#### LXI : LAN extension instrument based on IEEE1588

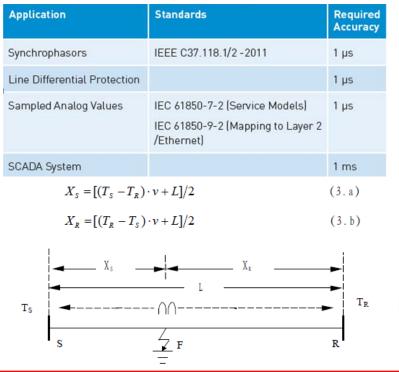

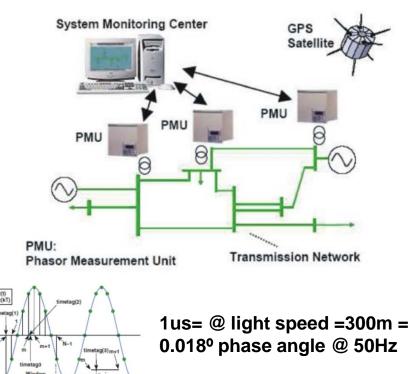

# **Smart Grid Application**

- Timing synchronization in power system consider in 4 categories:

- Less than 1µs: Traveling wave / light arrest fault allocation, EDI pharos sync (MPU) for power quality monitoring (smart grid)

- Less than 1ms: Fault recorder, and protection relay

- Less than 10ms : FTU、TTU、Smart grid power distributor

- 1 sec or above: SCADA

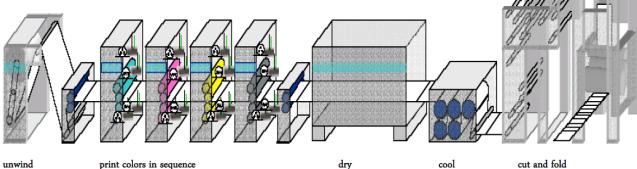

#### **Industrial Control** Example: Digital color offset printing

© MAN Rolan

- speed up to v = 20 m/s

- printing accuracy  $\Delta s = \pm 5 \ \mu m$

- synchronization requirement: Δs/v = ± 250 ns

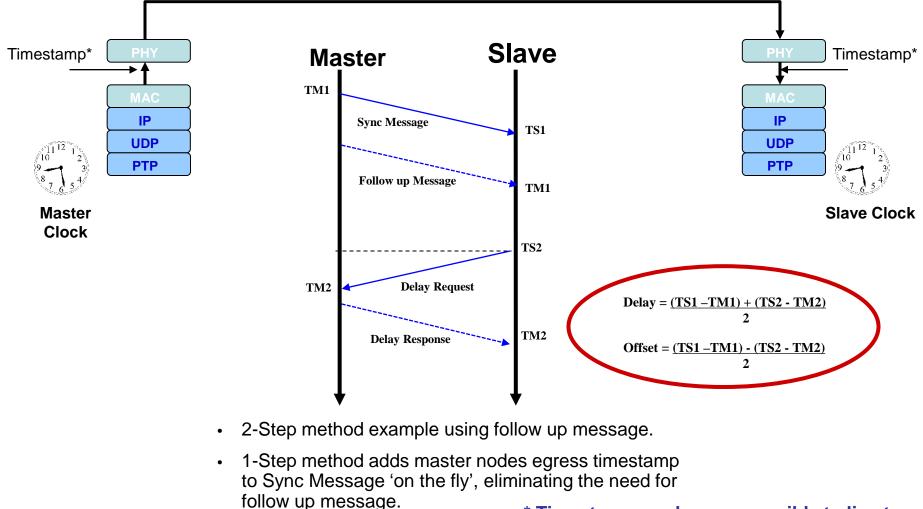

### **Basic IEEE1588 / 802.1AS MICROCHIP** Synchronization

\* Timestamp as close as possible to line to remove variable delays

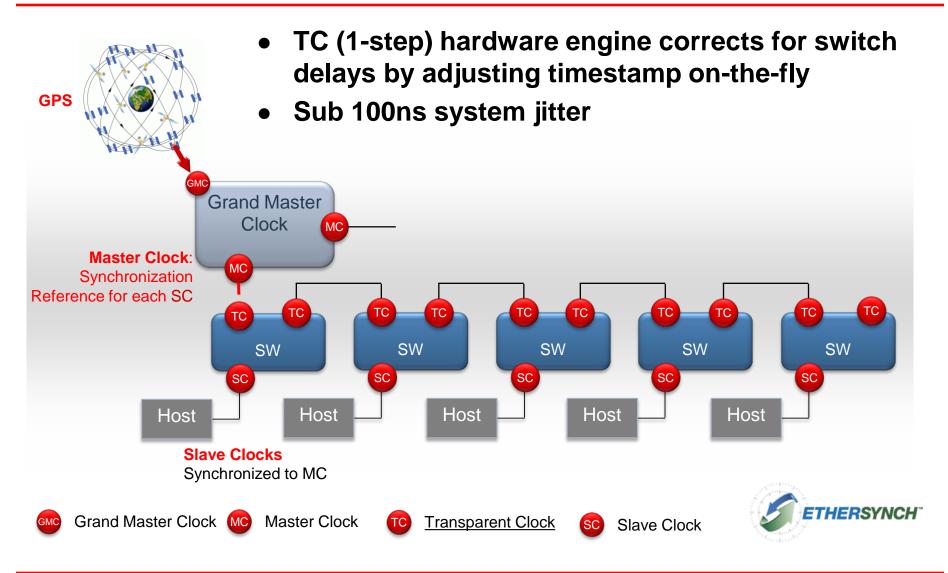

# Time Synchronization with EtherSynch<sup>®</sup>

- Supports ALL standards and features

- IEEE 1588-2008 Precision Time Protocol and IEEE 8021.AS (gPTP)\*

- Boundary or Transparent Clock with auto (hardware) correction

- Master and slave Ordinary Clock

- End-to-end and peer-to-peer

- 1 and 2 steps

- Multicast and unicast messaging

- IPv4/v6 and IEEE 802.3

- Packet filtering

- Synchronous Ethernet via recovered clock

### EtherSynch<sup>®</sup> Clock Synchronization

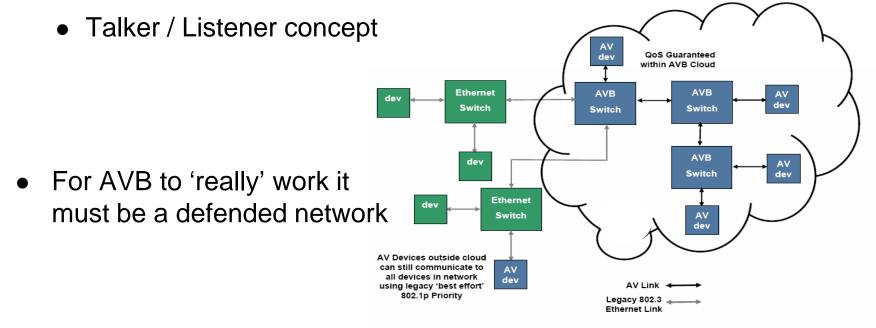

#### What is Ethernet AVB? (Audio Video Bridging)

- Supports audio & video (real-time) content over (packet based) Ethernet network

- Definable latencies and QoS even during congestion

- Guaranteed maximum 2ms delay over 7 hops

- Supports synchronized play back across many nodes

- Originally AVB Gen 2 renamed to 'Time Sensitive Networking'

- More appropriate not just A/V but stringent time critical control

- TSN is a collection of many specs  $\rightarrow$  'TSN toolbox'

- Select the necessary tools (specs) for the required task

- Specs include (continue to grow!)

- 802.1Qbv Time Aware Scheduling

- 802.1Qbu Frame Pre-emption

- 802.3br Interspersing Express Traffic

- 802.1Qch Cyclic Queuing & Forwarding

- 802.1Qci Ingress Policing

- 802.1Qca Path Control & Reservation

- 802.11CB Seamless Redundancy

# EtherSynch® MICROCHIP Deterministic Switch Engine

• AVB (Audio Video Bridging)

- Time synchronization, Stream Reservation, Traffic Shaper

- Time Aware Traffic Scheduler (Draft 802.1Qbv)

- Periodic scheduling reserved for timecritical class traffic

- Time sensitive Control

#### Low Latency

- 'Smart' cut-through Time-Aware traffic forwarding

- 64-byte 'store-and-stream'

- 10X Switch latency reduction

- Eg.<1uS for GigE

Synchronization in industrial 4.0 IEEE1588, redundancy and EtherCAT®

Programmable cycle time 8ns – 4.29s

Other Traffic

AVB, Best Effort)

Guard

Band

Time Aware

Traffic

**Other Traffic**

AVB, Best Effort)

Guard

Band

Traffic

Scheduling

Time Aware

Traffic

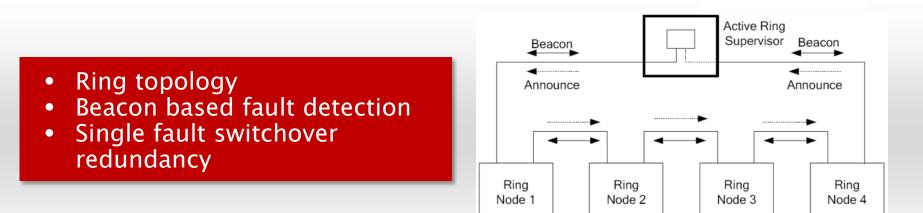

### Network Fault Recovery (DLR)

#### • Device Layer Ring (DLR)

- Ring Supervisor and Ring Node support

- Store / send programmable periodic Beacon frames (supervisor)

- Loss of Beacon packet detection (supervisory & node)

- Fast flush MAC table entries

- Free library available via product page

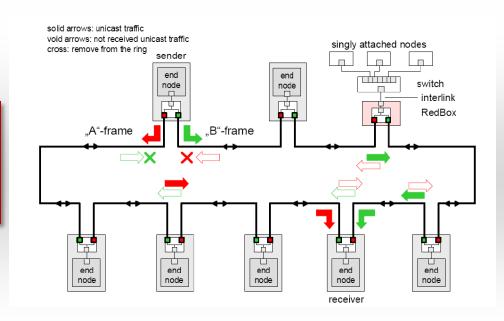

### Network Fault Recovery (HSR)

#### • High Seamless Redundancy (HSR)

- HSR packet duplication

- Duplicate HSR packet discard

- 256 HSR node ring support

- Free library available via product page

IEC 62439-3 CI. 5 HSR - High-availability Seamless Redundancy

- Ring topology

- Duplicated packet redundancy

- Single fault seamless (instant) switchover

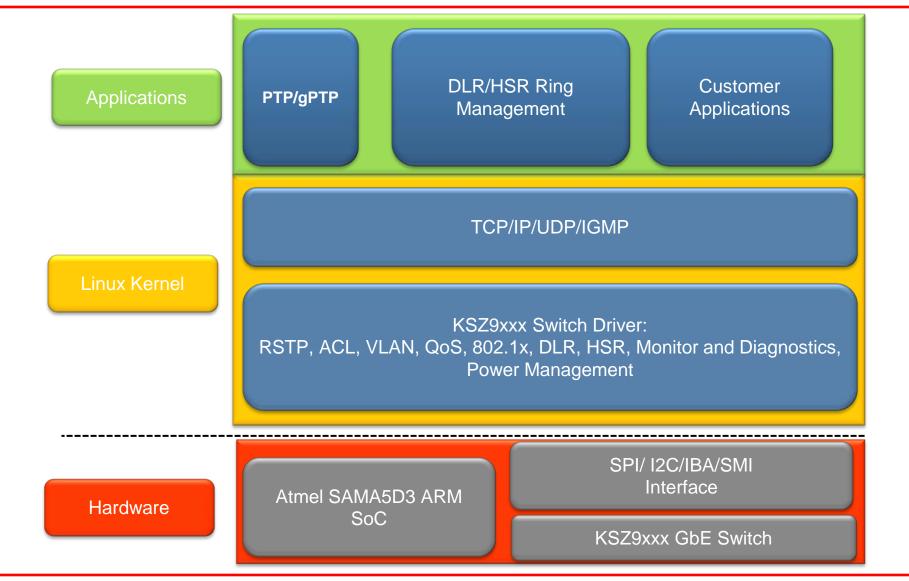

### **EVB Software Stack**

#### 3-Port 10/100 Switch Selector

| Product               | KSZ8863                          | KSZ8873        | KSZ8463        | LAN9303                  | LAN9353                          | LAN9354        | LAN9355              |

|-----------------------|----------------------------------|----------------|----------------|--------------------------|----------------------------------|----------------|----------------------|

| Ethernet<br>Bandwidth | 10Base-T/ 100Base-TX /100Base-FX |                |                | 10Base-T /<br>100Base-TX | 10Base-T/ 100Base-TX /100Base-FX |                |                      |

| Interface             |                                  |                | MII / RMII     |                          | RMII                             | MII            |                      |

| Wake-on-LAN           |                                  |                | Yes            |                          | Yes                              | Yes            | Yes                  |

| EEE                   |                                  |                | Yes            |                          | Yes                              | Yes            | Yes                  |

| Vdd IO                | 1.8/2.5/3.3                      | 1.8/2.5/3.3    | 1.8/2.5/3.3    | 3.3                      | 1.6-3.3                          | 1.6-3.3        | 1.6-3.3              |

| LinkMD<br>Cable Diag  | Yes                              | Yes            | Yes            |                          | Yes                              | Yes            | Yes                  |

| IEEE 1588             |                                  |                | Yes            |                          | Yes                              | Yes            | Yes                  |

| Power<br>Consumption* | 520mW<br>Total                   | 520mW<br>Total | 330mW<br>Total | 640mW<br>Total           | 555mW<br>Total                   | 555mW<br>Total | 555mW<br>Total       |

| Packages              | 48/LQFP                          | 64/LQFP        | 64/LQFP        | 56/QFN                   | 64/ QFN,<br>64/ TQFP             | 56/ QFN,       | 88/ QFN,<br>80/ TQFP |

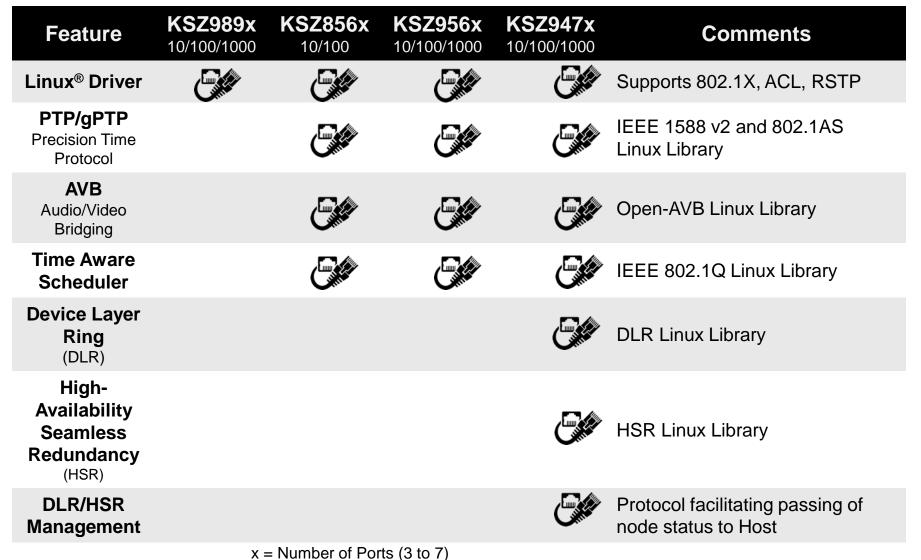

### AVB Switch MICROCHIP Software Enabled Features

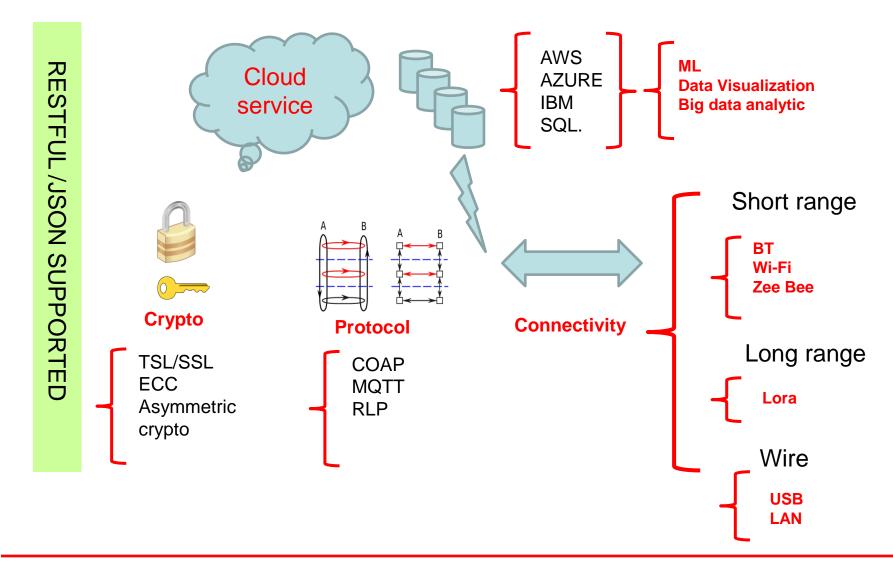

## **Microchip IoT View**

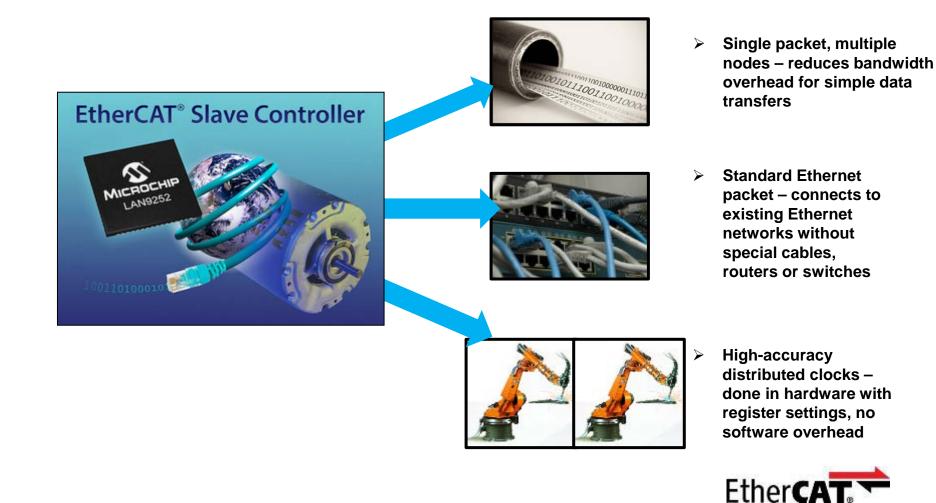

### EtherCAT<sup>®</sup> Synchronization

- Distributed clock is a synchronization method in EtherCAT

- Total 64-bit

- Microchip's LAN9252 is a EtherCAT slave controller, it supports DC

- Use Sync & Latch pin and DC unit to sync with each slave node

# **DC And Synchronization**

- Distributed clock (DC) in EtherCAT is to sync each salve node to a common clock , normally, the first slave's time as the Reference clock

- DC provide following functions

- System time : From 2000.1.1+500 yeas(64-bit @ "ns" ) Or 4.2S (32-bit @ "ns" )

- Reference clock

- Calculation drift, compensation, wire delay offset ...

- DC can sync each slave's OUTPUT/ INPUT into different synchronization modes

- No Sync →Free Run

- Sync with Jitter  $\rightarrow$  Sync to Sync manager

- Precise Sync  $\rightarrow$  Sync to DC

| 同期模式    | 内容         | 同期方法                      | 特征                                                                       |  |

|---------|------------|---------------------------|--------------------------------------------------------------------------|--|

| DC      | SYNCO 事件同期 | 以第1轴的时间为基准<br>同期其他从站的时间信息 | ・高精度<br>・需要在主站側进行补偿处理                                                    |  |

| SM2     | SM2 事件同期   | RxPDO 的收信时间同期             | <ul> <li>・没有传送延时补偿精度差</li> <li>・一定要在上位控制器侧保证传送时间<br/>(专用的硬件等)</li> </ul> |  |

| FreeRun | 非同期        | 非同期                       | ・处理简单<br>・欠缺实时性                                                          |  |

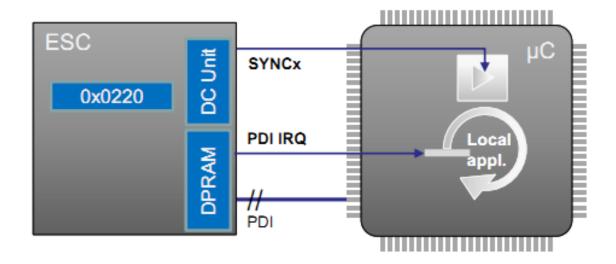

# MICROCHIP Synchronization with SOC

- Synchronization with Distributed Clock

- Local application in µC can be triggered by PDI IRQ or polling the SM-Event Register

- Setting of Outputs or latching of inputs shall be triggered by Sync0-Signal from ESC

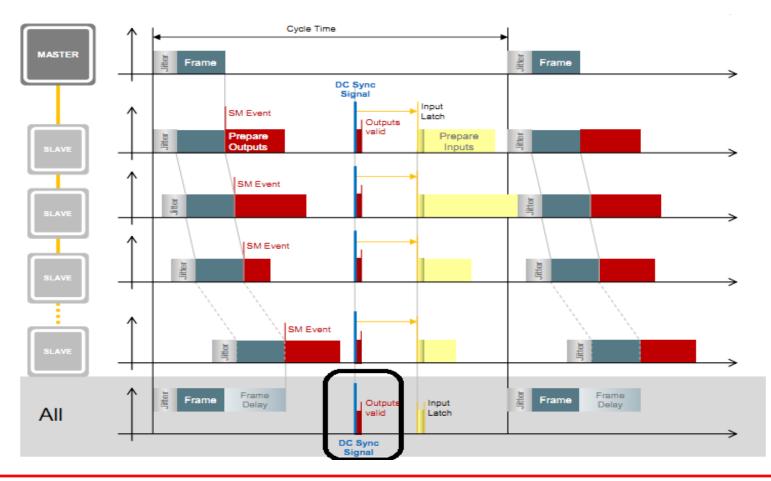

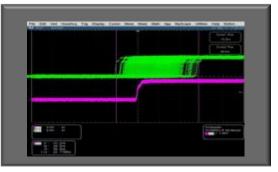

# **Synchronization - Enabled**

- With Sync enabled, outputs valid from each slave at same time.

- Precise synchronization achieved between all slaves (<<1us)

### **Ethernet Products**

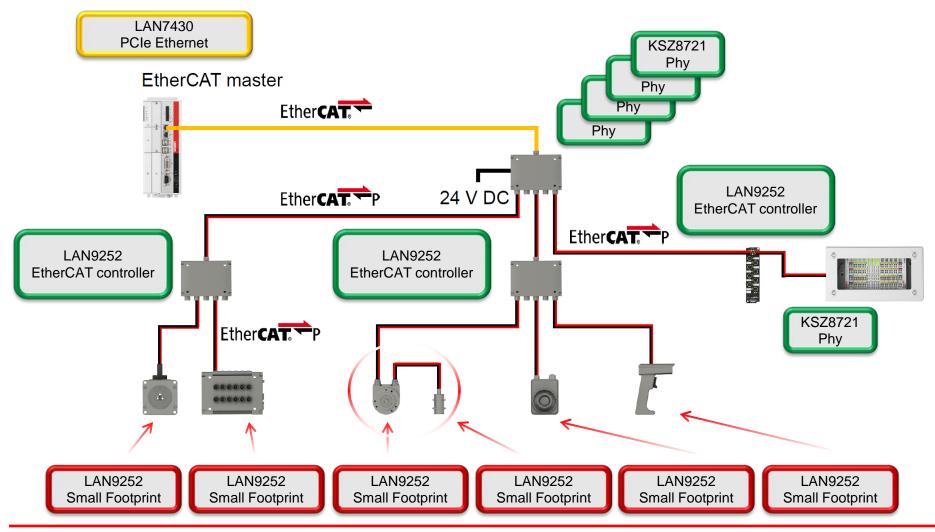

### EtherCAT<sup>®</sup> Industrial Solution

#### To Be Continued... Time Sensitive Network

# **Microchip Resources**

Microchip 工程師社區 <u>http://www.microchip.com.cn/community</u>

http://www.microchip.com.cn/community/html/newsletter.shtml

Weibo.com/microchiptech

t.qq.com/microchiptech

http://i.youku.com/Microchip

https://www.youtube.com/playlist?list=PLE B6441B0D29C405B

#### 聯繫信息

Microchip 台灣分公司 電郵:rtc.taipei@microchip.com 技術支援專線:0800-717-718 聯絡電話:

- •新竹 (03) 577-8366 •

- 高雄 (07) 213-7830

- 台北 (02) 2508-8600

### **Additional Slides**

#### V1 / V2 difference

| Criteria                                  | PTPv1                                                            | PTPv2                                                                                                                                             |  |  |

|-------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| clock types                               | Ordinary Clock (OC)<br>Boundary Clock (BC)                       | Ordinary Clock (OC)<br>Boundary Clock (BC)<br>end-to-end Transparent Clock (e2e TC)<br>peer-to-peer Transparent Clock (p2p TC)<br>Management Node |  |  |

| time representation                       | epoc number (16 bit)<br>seconds (32 bit)<br>nanoseconds (32 bit) | seconds (48 bit)<br>nanoseconds (32 bit)                                                                                                          |  |  |

| time interval resolution 1 ns             |                                                                  | 2 <sup>-16</sup> ns (15.26 fs)                                                                                                                    |  |  |

| message types                             | Sync<br>Follow_Up<br>Delay Reg                                   | Announce<br>Sync<br>Follow_Up<br>Delay Reg                                                                                                        |  |  |

|                                           | Delay_Resp                                                       | Delay Resp                                                                                                                                        |  |  |

|                                           | Management                                                       | Management                                                                                                                                        |  |  |

|                                           |                                                                  | Pdelay_Req<br>Pdelay_Resp<br>Pdelay_Resp_Follow_Up                                                                                                |  |  |

|                                           |                                                                  | Signaling                                                                                                                                         |  |  |

| message rates                             | small choice                                                     | bigger range and selectable per message type                                                                                                      |  |  |

| addressing                                | multicast                                                        | multicast<br>unicast                                                                                                                              |  |  |

| mappings UDP/IPv4 over IEEE 802.3         |                                                                  | UDP/IPv4 over IEEE 802.3<br>UDP/IPv6 over IEEE 802.3<br>directly over IEEE 802.3<br>PROFINET<br>DeviceNet/ControlNet                              |  |  |

| extensions                                | none                                                             | by Type/Length/Value (TLV)                                                                                                                        |  |  |

| redundancy BMC                            |                                                                  | BMC, Alternate Master, Master Cluster                                                                                                             |  |  |

|                                           | no                                                               | yes                                                                                                                                               |  |  |

| multiple domains by 4 multicast addresses |                                                                  | by Domain Number (8 bit)                                                                                                                          |  |  |

| What else?                                |                                                                  | profiles                                                                                                                                          |  |  |

|                                           |                                                                  | unicast message negotiation                                                                                                                       |  |  |

|                                           |                                                                  | security protocol (experimental)                                                                                                                  |  |  |

Table 1: PTPv1 / PTPv2 comparison

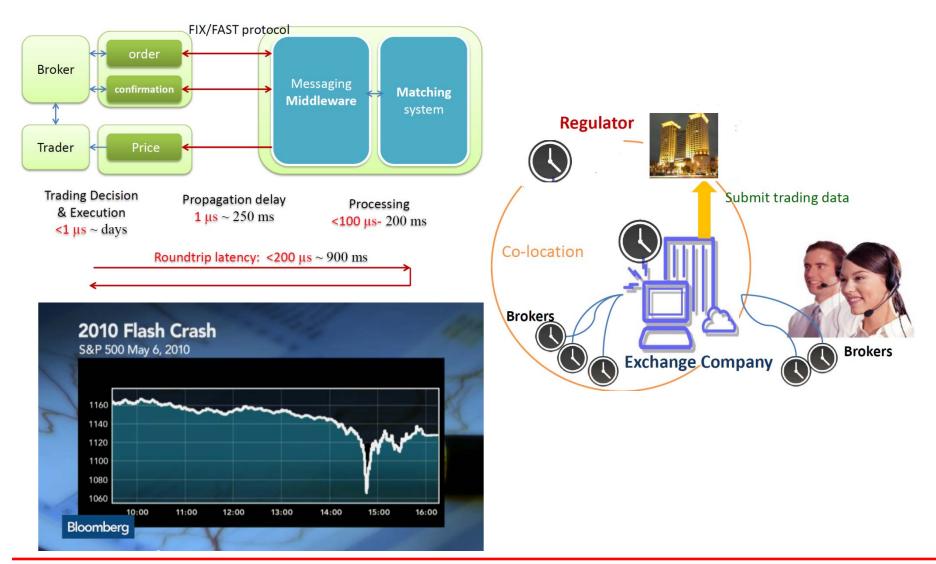

### What That Means

# **Stock Market Application**

### Advanced Ethernet Technology

#### • Energy Efficiency

- Ultra-Low Power, Patented Ethernet PHY

- EtherGREEN™ Platform Advanced Power Management

- Ultra-Deep-Sleep uA Standby

####

#### • Deterministic

- EtherSynch<sup>®</sup> Platform IEEE 1588v2/802.1AS Synchronization

- Fixed / Low-Latency Transmission

- AVB / Time-Aware Traffic Scheduling

#### • Reliability

- Quiet-WIRE<sup>®</sup> Technology Enhanced EMC Performance

- LinkMD<sup>®</sup>+ Diagnostics (Link Quality Indicator)

- Network Fault Recovery Hardware Engine

<sup>\*</sup> August 2015 Micrel Acquisition

### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A. Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies. © 2017 Microchip Technology Incorporated, All Rights Reserved.