Page 47 - 軟體定義汽車時代變的何止是車

P. 47

DESIGN CORNER

表現為元件閾值電壓的意外偏移 和汲極電流的降低。對於這些矽 基元件而言,PBTI歸咎於閘極介 電質中電子阱(electron traps)的 存在,會從元件傳導通道捕捉電荷 載子(charge carriers)。

45

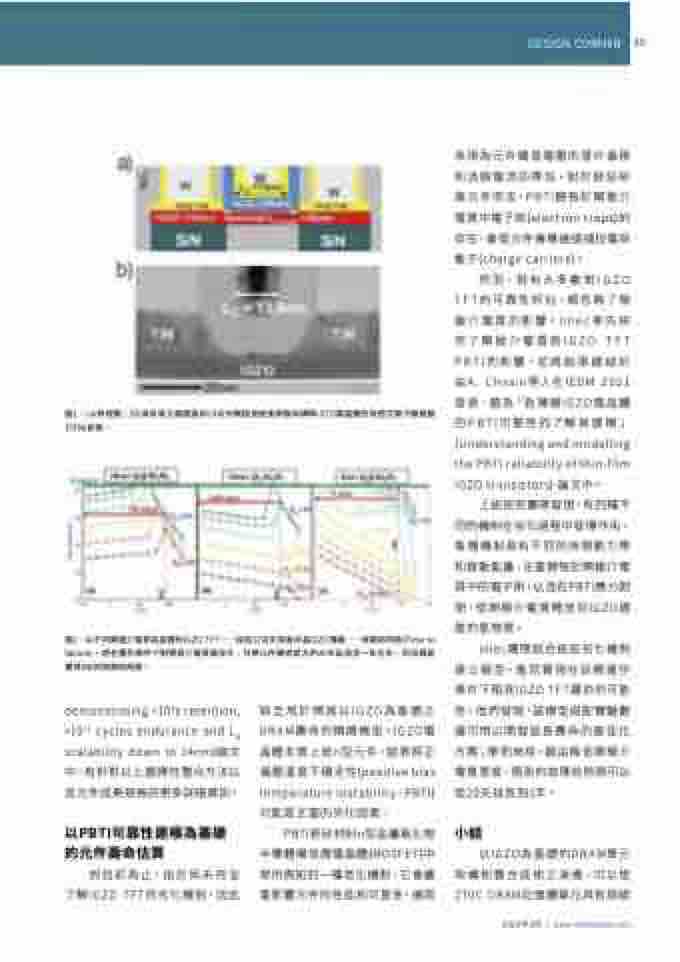

圖1:(a)原理圖;(B)具有氧化層隧道和14奈米閘極長度後閘極架構單IGZO電晶體的穿透式電子顯微鏡 (TEM)影像。

圖2:以不同閘極介電質為基礎的IGZO TFT──採用12奈米厚度非晶IGZO薄膜──故障前時間(Time to failure)。透在運作條件下對閘極介電質最佳化,可將元件壽命從大約20天延長至一年左右,而目標是 實現5年的故障前時間。

demonstrating >103s retention, >1011 cycles endurance and Lg scalability down to 14nm)論文 中,有針對以上選擇性整合方法以 及元件成果規格的更多詳細資訊。

然而,現有大多數對IGZO TFT的可靠性評估,都忽略了閘 極介電質的影響。Imec率先研 究了閘極介電質對IGZO TFT PBTI的影響,並將結果總結於 由A. Chasin等人在IEDM 2021 發表、題為「對薄膜IGZO電晶體 的PBTI可靠性的了解與建模」 (Understanding and modelling the PBTI reliability of thin-film IGZO transistors) 論文中。

以PBTI可靠性建模為基礎 的元件壽命估算

PBTI是矽材料n型金屬氧化物 半導體場效應電晶體(MOSFET)中 眾所周知的一種老化機制,它會嚴 重影響元件的性能和可靠性,通常

小結

到目前為止,由於尚未完全 了解IGZO TFT的劣化機制,因此

以IGZO為基礎的DRAM單元 架構和整合技術之演進,可以使 2T0C DRAM記憶體單元具有超過

缺乏用於預測以IGZO為基礎之 DRAM壽命的精確模型。IGZO電 晶體本質上是n型元件,這表明正 偏壓溫度不穩定性(positive bias temperature instability,PBTI) 可能是主要的劣化因素。

imec團隊結合這些劣化機制 建立模型,進而實現在目標運作 條件下預測IGZO TFT壽命的可能 性。他們發現,該模型搭配實驗數 據可用以開發延長壽命的最佳化 方案;舉例來說,藉由降低閘極介 電質厚度,預測的故障前時間可以 從20天延長到1年。

上述研究團隊發現,有四種不 同的機制在劣化過程中發揮作用, 每種機制具有不同的時間動力學 和啟動能量,主要歸咎於閘極介電 質中的電子阱,以及在PBTI應力期 間,從閘極介電質釋放到IGZO通 道的氫物質。

2022年3月 | www.eettaiwan.com