Page 51 - 異質整合當道 材料接合應力強度備受矚目

P. 51

DESIGN CORNER

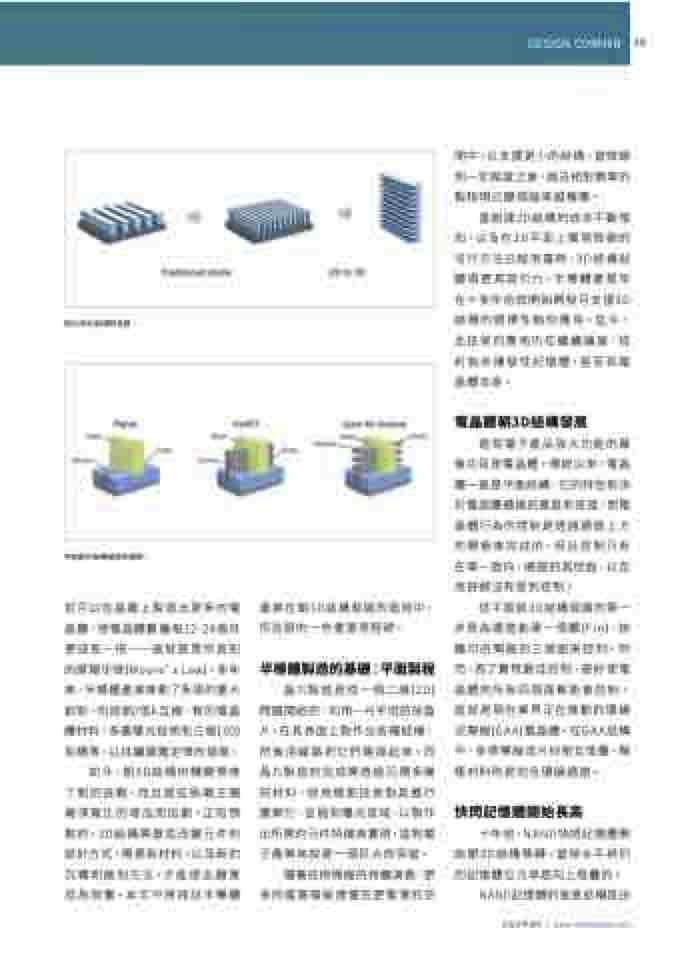

從2D到3D結構的發展。

當創建2D結構的成本不斷增 加,以及在2D平面上實現微縮的 可行方法已經用盡時,3D結構就 變得更具吸引力。半導體產業早 在十多年前就開始開發可支援3D 結構的選擇性蝕刻應用。迄今, 此技術的應用仍在繼續擴展,從 封裝非揮發性記憶體,甚至到電 晶體本身。

平面朝3D結構發展的過程。

造就電子產品強大功能的幕 後功臣是電晶體。傳統以來,電晶 體一直是平面結構,它的特性取決 於電晶體通道的寬度和長度,而電 晶體行為的控制是透過通道上方 的閘極來完成的。但此控制只有 在單一面向,通道的其他面,以及 底部都沒有受到控制。

就可以在晶圓上製造出更多的電 晶體,使電晶體數量每12~24個月 便成長一倍——這就是眾所皆知 的摩爾定律(Moore’s Law)。多年 來,半導體產業推動了多項的重大 創新,包括銅/低k互連、新的電晶 體材料、多重曝光技術和三維(3D) 架構等,以持續摩爾定律的發展。

產業在朝3D結構發展的過程中, 所克服的一些重要里程碑。

晶片製造是從一個二維(2D) 問題開始的:利用一片平坦的矽晶 片,在其表面上製作出各種結構, 然後用線路把它們連接起來。而 晶片製造的完成需透過沉積多層 的材料,使用微影技術對其進行 圖案化,並蝕刻曝光區域,以製作 出所需的元件特徵來實現,這對電 子產業來說是一個巨大的突破。

從平面朝3D結構發展的第一 步是為通道創建一個鰭(Fin),該 鰭可由閘極的三個面來控制。然 而,為了實現最佳控制,最好使電 晶體的所有四個面都能被控制, 這就是現在業界正在推動的環繞 式閘極(GAA)電晶體。在GAA結構 中,多條導線或片材相互堆疊,閘 極材料則是完全環繞通道。

如今,朝3D結構的轉變帶來 了新的挑戰,而且這些挑戰正隨 著深寬比的增加而加劇。正如預 期的,3D結構需徹底改變元件的 設計方式,需要新材料,以及新的 沉積和蝕刻方法,才能使此願景 成為現實。本文中將探討半導體

快閃記憶體開始長高

半導體製造的基礎:平面製程

隨著技術微縮的持續演進,更 多的電路需被建置在更緊湊的空

十年前,NAND快閃記憶體開 始朝3D結構移轉,當時水平排列 的記憶體位元串是向上堆疊的。

間中,以支援更小的結構。當微縮 到一定程度之後,過去相對簡單的 製程現已變得越來越複雜。

電晶體朝3D結構發展

NAND記憶體的垂直結構是由 2022年8月 | www.eettaiwan.com

49