Page 53 - RISC-V創新百花齊放中國MCU業者積極佈局

P. 53

DESIGN CORNER

高的通道電阻,要克服這個問題, 設計上會使用較薄的閘極氧化絕 緣層,使其具有較低的閘極臨界 電壓(~2V),進而能降低通道電 阻,這也是平面式結構功率晶體的 特徵之一。在實務使用上,建議使 用者在設計驅動電路時,截止時驅 動電壓採用負電壓,用於避免驅動 時的誤動作造成功率晶體燒毀, 反之,在溝槽式結構的SiC功率晶

體因其具有較高的閘極臨界電壓 (>4V),無論那一種電路結構,都 不需要使用負電壓驅動。

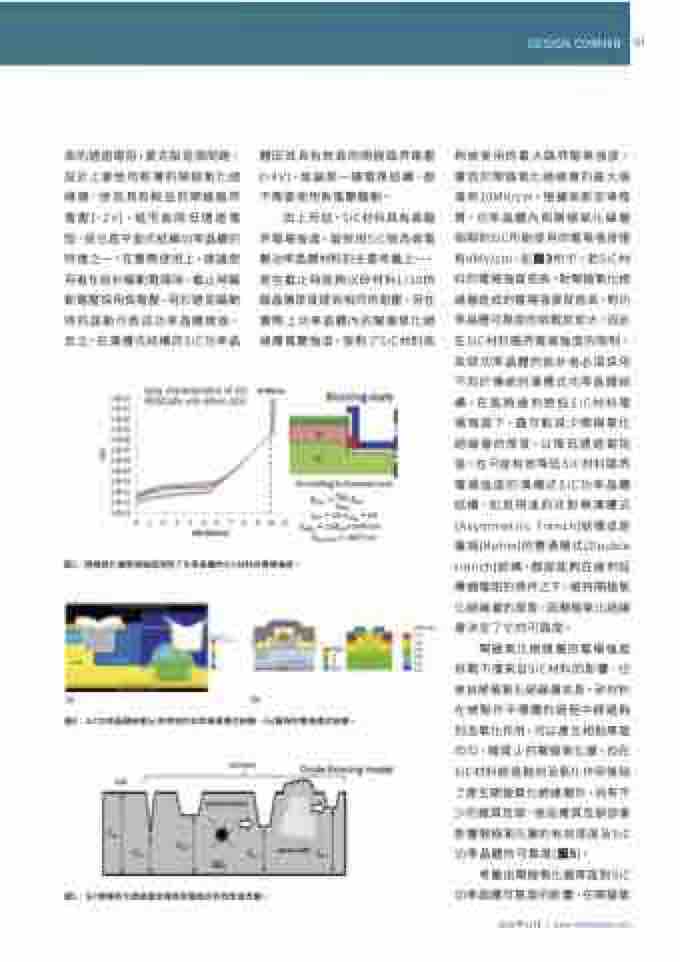

夠被使用的最大臨界電場強度, 肇因於閘極氧化絕緣層的最大值 僅有10MV/cm。根據高斯定律推 算,功率晶體內與閘極氧化緣層 相鄰的SiC所能使用的電場強度僅 有4MV/cm,如圖3所示。若SiC材 料的電場強度愈高,對閘極氧化絕 緣層造成的電場強度就愈高,對功 率晶體可靠度的挑戰就愈大,因此 在SiC材料臨界電場強度的限制, 致使功率晶體的設計者必須採用 不同於傳統的溝槽式功率晶體結 構,在能夠達到更低SiC材料電 場強度下,盡可能減少閘極氧化 絕緣層的厚度,以降低通道電阻 值。在可能有效降低SiC材料臨界 電場強度的溝槽式SiC功率晶體 結構,如英飛凌的非對稱溝槽式 (Asymmetric Trench)結構或是 羅姆(Rohm)的雙溝槽式(Double trench)結構,都是能夠在達到低 導通電阻的條件之下,維持閘極氧 化絕緣層的厚度,因閘極氧化絕緣 層決定了它的可靠度。

圖3:閘極氧化層電場強度限制了功率晶體內SiC材料的電場強度。

(a) (b) 圖4:SiC功率晶體結構(a)英飛凌的非對稱溝槽式結構、(b)羅姆的雙溝槽式結構。

閘極氧化絕緣層的電場強度 挑戰不僅來自SiC材料的影響,也 來自閘極氧化絕緣層本身。矽材料 在被製作半導體的過程中經過蝕 刻及氧化作用,可以產生相對厚度 均勻、雜質少的閘極氧化層,但在 SiC材料經過蝕刻及氧化作用後除 了產生閘極氧化絕緣層外,尚有不 少的雜質及碳,這些雜質及碳卻會 影響閘極氧化層的有效厚度及SiC 功率晶體的可靠度(圖5)。

如上所述,SiC材料具有高臨 界電場強度,當採用SiC做為高電 壓功率晶體材料的主要考量之一, 是在截止時能夠以矽材料1/10的 磊晶層厚度達到相同的耐壓,但在 實際上功率晶體內的閘極氧化絕 緣層電壓強度,限制了SiC材料能

51

圖5:SiC閘極氧化絕緣層受雜質影響造成有效厚度改變。

考量由閘極氧化層厚度對SiC 功率晶體可靠度的影響,在閘極氧

2021年11月 | www.eettaiwan.com