Page 51 - RISC-V創新百花齊放中國MCU業者積極佈局

P. 51

DESIGN CORNER

• SiC MOSFET:9.9mΩ 在SPICE模擬中,用於計算效

率的指令如下:

.meas TRAN Effic1 AVG

(abs(V(N001,N005)*I(R2)))/((ab s(V(N001)*I(V3)))+(abs(V(N009 )*I(V4))))*100

.meas TRAN Effic2 AVG abs(V(N002,N006)*I(R4))/ abs(V(N002)*I(V5))*100

.meas TRAN Effic3 AVG abs(V(N003,N007)*I(R1))/ abs(V(N003)*I(V1))*100

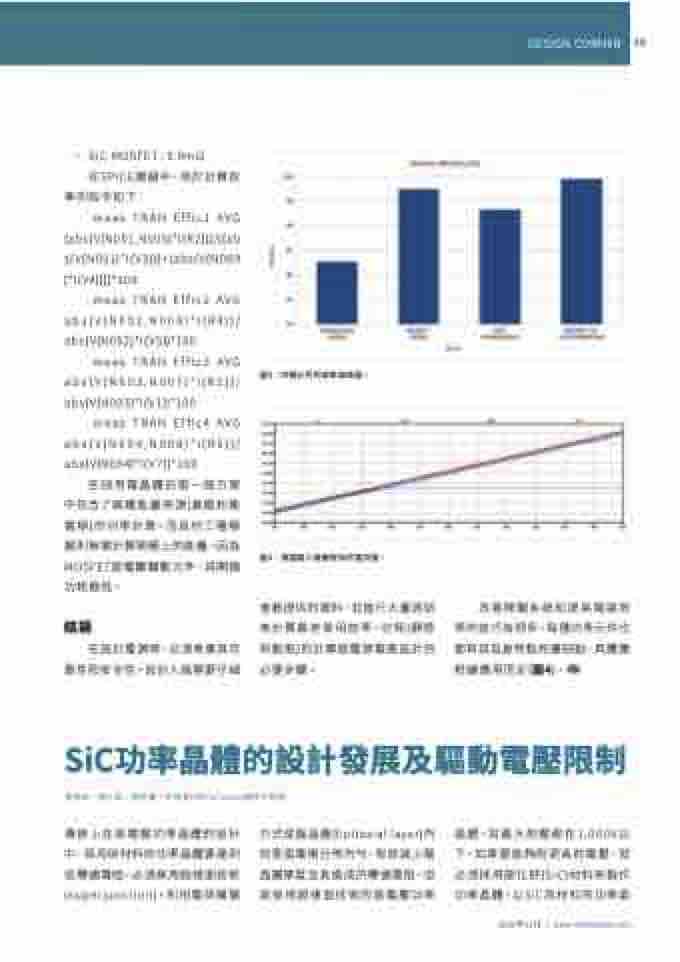

圖3:四種元件的效率直條圖。

.meas TRAN Effic4 AVG abs(V(N004,N008)*I(R5))/ abs(V(N004)*I(V7))*100

49

在採用電晶體的第一個方案 中包含了兩種能量來源(基極和集 電極)的功率計算。而其他三種模 擬則無需計算閘極上的能量,因為 MOSFET是電壓驅動元件,其閘極 功耗極低。

圖4:掃描輸入電壓得到的電流圖。

查看提供的資料,並進行大量測試 來計算最差使用效率,功耗(靜態 和動態)的計算是電源電路設計的 必要步驟。

改善開關系統和提高電路效 率的技巧有很多,每種功率元件也 都有其自身特點和優缺點,具體應 根據應用而定(圖4)。

結語

在設計電源時,必須考慮其可 靠性和安全性。設計人員需要仔細

SiC功率晶體的設計發展及驅動電壓限制

張家瑞、黃正斌、張哲睿,英飛凌科技(Infineon)應用工程師

傳統上在高電壓功率晶體的設計 中,採用矽材料的功率晶體要達到 低導通電阻,必須採用超接面技術 (superjunction)。利用電荷補償

方式使磊晶層(Epitaxial layer)內 的垂直電場分佈均勻,有效減少磊 晶層厚度及其造成的導通電阻,但 是採用超接面技術的高電壓功率

晶體,其最大耐壓都在1,000V以 下,如果要能夠耐更高的電壓,就 必須採用碳化矽(SiC)材料來製作 功率晶體,以SiC為材枓的功率晶

2021年11月 | www.eettaiwan.com