Page 52 - RISC-V創新百花齊放中國MCU業者積極佈局

P. 52

50

體,在 S i C 的 高 臨 界 電 場 強 度 之 下, 即使相同耐壓條件之下,其磊晶層 的厚度約為矽材料的1/10,進而使 其所造成的導通電阻能夠有效被 降低,達到高耐壓低導通電阻的 基本要求。

在矽材料的高壓超接面功率 晶體中,磊晶層的導通電阻佔總導 通電阻的90%以上,所以只要減少 磊晶層造成的導通電阻,就能有效 降低總導通電阻值;而SiC功率晶 體依照不同耐電壓等級,通道電阻 (Channel resistance,Rch)佔總導 通電阻具有不同的比值,例如,在 650V的SiC功率晶體中,通道電 阻佔總導通電阻達50%以上,因 此要有效降低總導通電阻的最直 接方向是改善通道電阻值。由通 道電阻的公式,如公式(1)可以觀 察到,有效降低通道電阻的方法 有幾個方向:減少通道長度L、減 少閘極氧化層厚度dox、提高通道 寬度W、提高通道的電子移動率 μch、降低通道導通臨界電壓VT、 或是提高驅動電壓VGS,然而這幾 項可能的方向,分別都有各自的限 制情況出現。

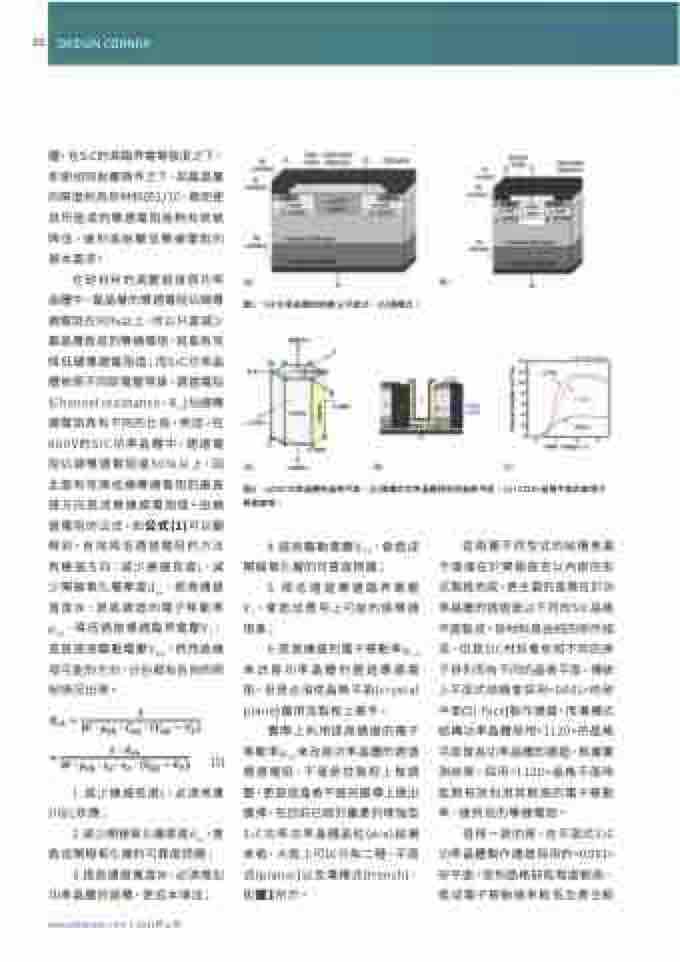

(a) (b) 圖1:SiC功率晶體的結構(a)平面式、(b)溝槽式。

(a) (b) (c)

圖2:(a)SiC功率晶體的晶格平面、(b)溝槽式功率晶體採用的晶格平面、(c)<1120>晶格平面的高電子 移動速率。

4.提高驅動電壓VGS,會造成 閘極氧化層的可靠度問題;

這兩種不同型式的結構差異 不僅僅在於閘極是否以內嵌的型 式製造而成,更主要的差異在於功 率晶體的通道是以不同的SiC晶格 平面製成。矽材料是由純的矽所組 成,但是SiC材料會依照不同的原 子排列而有不同的晶格平面,傳統 上平面式結構會採用<0001>的矽 平面(Si-face)製作通道,而溝槽式 結構功率晶體採用<1120>的晶格 平面做為功率晶體的通道,根據實 測結果,採用<1120>晶格平面時 能夠有效利用其較高的電子移動 率,達到低的導通電阻。

5.降低通道導通臨界電壓 VT,會造成應用上可能的誤導通 現 象;

6.提高通道的電子移動率μch 來改善功率晶體的通道導通電 阻,但是必須從晶格平面(crystal plane)選用及製程上著手。

1.減少通道長度L,必須考慮 DIBL效應;

2.減少閘極氧化層厚度dox,會 造成閘極氧化層的可靠度問題;

值得一提的是,在平面式SiC 功率晶體製作通道採用的<0001> 矽平面,受到晶格缺陷程度較高, 造成電子移動速率較低及產生較

3.提高通道寬度W,必須增加 功率晶體的面積,使成本增加;

www.eettaiwan.com | 2021年11月

(1)

實際上利用提高通道的電子 移動率μch來改善功率晶體的通道 導通電阻,不僅是從製程上做調 整,更是從晶格平面的選擇上做出 選擇,在目前已經的量產的增強型 SiC功率功率晶體晶粒(die)結構 來看,大致上可以分為二種,平面 式(planar)以及溝槽式(trench), 如圖1所示。

DESIGN CORNER