Page 53 - 第三代半導體—— 碳化矽材料製程與分析

P. 53

DESIGN CORNER

8所示的訊號。 當PWM_B輸入訊號被拉低

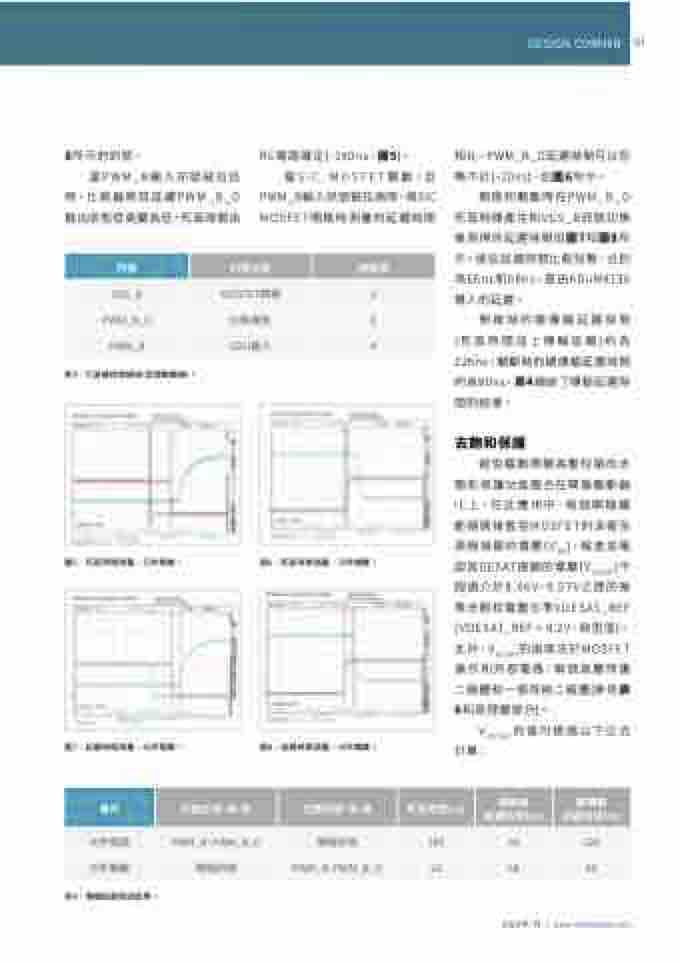

RC電路確定(~160ns,圖5)。 當SiC MOSFET關斷,且 PWM_B輸入訊號被拉高時,與SiC MOSFET開啟時測量的延遲時間

相比,PWM_B_D延遲時間可以忽 略不計(~20ns),如圖6所示。

時,比較器將其延遲PWM_B_D 輸出狀態從高變為低,死區時間由

開啟和關斷時在PWM_B_D 死區時間產生和VGS_B訊號切換 後測得的延遲時間如圖7和圖8所 示。這些延遲時間比較短暫,分別 為66ns和68ns,是由ADuM4136 導入的延遲。

51

符號

訊號功能

通道號

VGS_B

MOSFET閘極

2

PWM_B_D

比較器後

3

PWM_B

GDU輸入

4

表3:示波器訊號描述(低端驅動器)。

開啟時的總傳輸延遲時間 (死區時間加上傳輸延遲)約為 226ns,關斷時的總傳輸延遲時間 約為90ns,表4總結了傳輸延遲時 間的結果。

圖5:死區時間測量,元件開啟。

圖6:死區時間測量,元件關斷。

圖8:延遲時間測量,元件關斷。

避免驅動開關高壓短路的去 飽和保護功能整合在閘極驅動器 IC上。在此應用中,每個閘極驅 動器間接監控MOSFET的汲極至 源極接腳的電壓(VDS),檢查並確 認其DESAT接腳的電壓(VDESAT)不 超過介於8.66V~9.57V之間的基 準去飽和電壓位準VDESAT_REF (VDESAT_REF = 9.2V,典型值)。 此外,VDESAT的值取決於MOSFET 操作和外部電路:兩個高壓保護 二極體和一個齊納二極體(參見表 6和原理圖部分)。

去飽和保護

圖7:延遲時間測量,元件開啟。

VDESAT的值可透過以下公式 計算:

事件

切換訊號,高-低

切換訊號,低-高

死區時間(ns)

驅動器 延遲時間(ns)

總傳輸 延遲時間(ns)

元件開啟

PWM_B、PWM_B_D

閘極訊號

160

66

226

元件關斷

閘極訊號

PWM_B、PWM_B_D

22

68

90

表4:傳播延遲測試結果。

2022年7月 | www.eettaiwan.com