Page 54 - 第三代半導體—— 碳化矽材料製程與分析

P. 54

52

VDESAT= VZ + 2 × VDIODE_DROP + VDS

釋放,兩個保護二極體正向偏 置,齊納二極體出現故障。在這 裡,VDESAT電壓是否超出VDESAT_ REF值取決於VDS的值。

去飽和MOSFET,同時生成延遲 < 2μs的FAULT訊號,使閘極驅動 器訊號(VGS)立即鎖定,這些訊號 只能由RESET接腳解鎖。

其中:VZ是齊納二極體擊穿 電壓,VDIODE_DROP是每個保護二極 體的正向壓降。

正常工作時,VDS和VDESAT電壓 一直很低。當高電流流經MOSFET 時,VDS電壓增大,導致VDESAT電壓 位準升至VDESAT_REF以上。在 這種情況下,閘極驅動器輸出接 腳(VOUT)在200ns內變為低位準並

檢測電壓位準取決於VDS的 值,並可透過選擇具有擊穿電壓 VZ的合適齊納二極體設定為任何 位準。反過來,可根據MOSFET製 造商數據手冊中所述的VDS來估計 用於去飽和的MOSFET電流(ID)。

在關斷期間,DESAT接腳在 內部被拉低,未發生飽和事件。 此外,MOSFET電壓(VMOSFET)高, 且兩個二極體反向偏置,以保護 DESAT接腳。在接通期間,DESAT 接腳在300ns內部消隱時間後

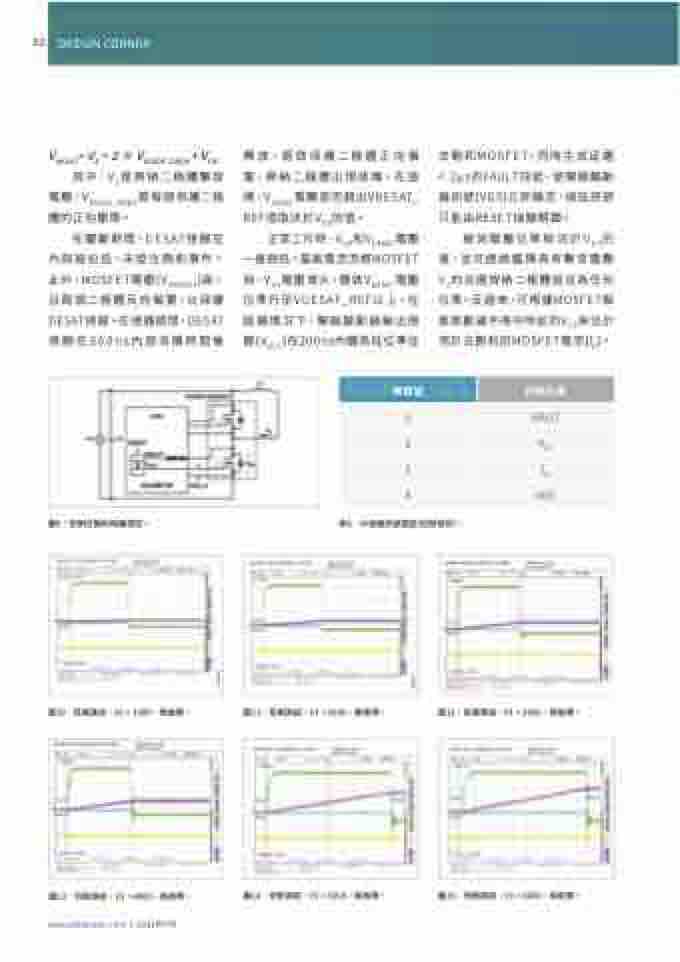

通道號

訊號名稱

1

FAULT

2

VDS

3

ID

4

VGS

圖9:低側去飽和保護測試。

表5:示波器訊號描述(低側測試)。

圖11:低側測試,V1 = 200V,無故障。 圖12:低側測試,V1 = 300V,無故障。

圖10:低側測試,V1 = 100V,無故障。

圖13:低側測試,V1 = 400V,無故障。

www.eettaiwan.com | 2022年7月

圖14:低側測試,V1 = 500V,無故障。 圖15:低側測試,V1 = 600V,無故障。

DESIGN CORNER