Page 47 - 歷經一番寒徹骨DDR5記憶體主流時代即將來臨?

P. 47

DESIGN CORNER

元設計中的單片式CFET與順序式 CFET作出了PPAC評估。

45

Ryckaert指出,從這個基準 來看,與導致有效電容上升的順序 流程相比,使用單片式製程流程 製造的CFET消耗的面積更少,性 能也更高。然而,透過以下三項最 佳化,可以將順序式CFET的軌跡 (trajectory)與單片式CFET的相提 並論。這三項最佳化為:

1. 自對準的閘極合併(圖2中的 v2);

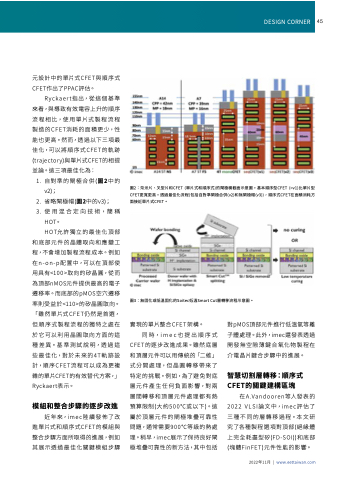

圖2:奈米片、叉型片和CFET (單片式和順序式)的閘極橫截面示意圖。基本順序型CFET (=v1)比單片型 CFET更寬更高。透過最佳化流程(包括自對準閘極合併(v2)和無閘極帽(v3)),順序式CFET在面積消耗方 面接近單片式CFET。

圖3:無固化或低溫固化的Soitec低溫Smart Cut層轉移流程示意圖。

2. 省略閘極帽(圖2中的v3);

3. 使用混合定向技術,簡稱

HOT。

HOT允許獨立的最佳化頂部 和底部元件的晶體取向和應變工 程,不會增加製程流程成本。例如 在n-on-p配置中,可以在頂部使 用具有<100>取向的矽晶圓,從而 為頂部nMOS元件提供最高的電子 遷移率。而底部的pMOS空穴遷移 率則受益於<110>的矽晶圓取向。 「雖然單片式CFET仍然是首選, 但順序式製程流程的獨特之處在 於它可以利用晶圓取向方面的這 種差異。基準測試說明,透過這 些最佳化,對於未來的4T軌跡設 計,順序CFET流程可以成為更複 雜的單片CFET的有效替代方案,」 Ryckaert表示。

實現的單片整合CFET架構。 同時,imec也提出順序式 CFET的逐步改進成果。雖然底層 和頂層元件可以用傳統的「二維」 式分開處理,但晶圓轉移帶來了 特定的挑戰。例如,為了避免對底 層元件產生任何負面影響,對兩 層間轉移和頂層元件處理都有熱 預算限制(大約500°C或以下)。這 屬於頂層元件的閘極堆疊可靠性 問題,通常需要900°C等級的熱處 理。稍早,imec展示了保持良好閘 極堆疊可靠性的新方法,其中包括

對pMOS頂部元件進行低溫氫等離 子體處理。此外,imec還發表透過 開發無空隙薄鍵合氧化物製程在 介電晶片鍵合步驟中的進展。

模組和整合步驟的逐步改進

在A.Vandooren等人發表的 2022 VLSI論文中,imec評估了 三種不同的層轉移過程。本文研 究了各種製程選項對頂部(絕緣體 上完全耗盡型矽(FD-SOI))和底部 (塊體FinFET)元件性能的影響。

近年來,imec陸續發佈了改 進單片式和順序式CFET的模組與 整合步驟方面所取得的進展,例如 其展示透過最佳化關鍵模組步驟

智慧切割層轉移:順序式 CFET的關鍵建構區塊

2022年11月 | www.eettaiwan.com