Page 48 - 歷經一番寒徹骨DDR5記憶體主流時代即將來臨?

P. 48

46

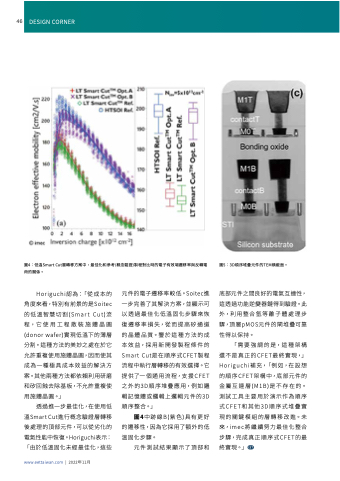

圖4:低溫Smart Cut層轉移方案中,最佳化和參考(概念驗證)製程對比時的電子有效場遷移率與反轉電 荷的關係。

圖5:3D順序堆疊元件的TEM橫截面。

Horiguchi認為:「從成本的 角度來看,特別有前景的是Soitec 的低溫智慧切割(Smart Cut)流 程,它使用工程散裝施體晶圓 (donor wafer)實現低溫下的薄層 分割。這種方法的美妙之處在於它 允許重複使用施體晶圓,因而使其 成為一種極具成本效益的解決方 案。其他兩種方法都依賴利用研磨 和矽回蝕去除基板,不允許重複使 用施體晶圓。」

元件的電子遷移率較低。Soitec進 一步完善了其解決方案,並顯示可 以透過最佳化低溫固化步驟來恢 復遷移率損失,從而提高矽通道 的晶體品質。鑒於這種方法的成 本效益,採用新開發製程條件的 Smart Cut是在順序式CFET製程 流程中執行層轉移的有效選擇。它 提供了一個通用流程,支援CFET 之外的3D順序堆疊應用,例如邏 輯記憶體或邏輯上邏輯元件的3D 順序整合。」

底部元件之間良好的電氣互連性, 這透過功能逆變器鏈得到驗證。此 外,利用整合氫等離子體處理步 驟,頂層pMOS元件的閘堆疊可靠 性得以保持。

透過進一步最佳化,在使用低 溫Smart Cut進行概念驗證層轉移 後處理的頂部元件,可以從劣化的 電氣性能中恢復。Horiguchi表示: 「由於低溫固化未經最佳化,這些

圖4中跡線B(紫色)具有更好 的遷移性,因為它採用了額外的低 溫固化步驟。

「需要強調的是,這種架構 還不是真正的CFET最終實現,」 Horiguchi補充,「例如,在設想 的順序CFET架構中,底部元件的 金屬互連層(M1B)是不存在的。 測試工具主要用於演示作為順序 式CFET和其他3D順序式堆疊實 現的關鍵模組的層轉移改進。未 來,imec將繼續努力最佳化整合 步驟,完成真正順序式CFET的最 終 實 現。」

www.eettaiwan.com | 2022年11月

元件測試結果顯示了頂部和

DESIGN CORNER