Page 56 - 歷經一番寒徹骨DDR5記憶體主流時代即將來臨?

P. 56

54

圖6:在測試頻率上利用PLZ303W對10mΩ DUT進行測量的結果。

圖7:用於離散式VCCS測試的電路圖。

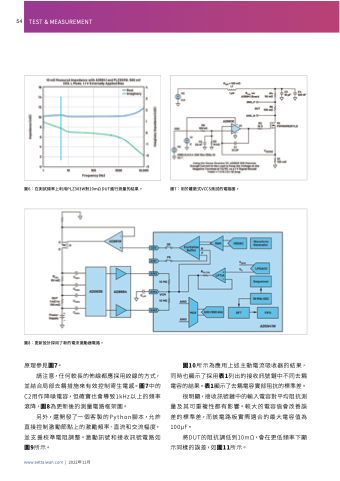

圖8:更新設計採用了新的電流激勵器電路。

原理參見圖7。 請注意,任何較長的佈線都應採用絞線的方式,

圖10所示為應用上述主動電流吸收器的結果, 同時也顯示了採用表1列出的接收訊號鏈中不同去耦 電容的結果。表1顯示了去耦電容實部阻抗的標準差。

並結合局部去耦措施來有效控制寄生電感。圖7中的 C2用作降噪電容,但確實也會導致1kHz以上的頻率 滾降,圖8為更新後的測量電路框架圖。

很明顯,接收訊號鏈中的輸入電容對平均阻抗測 量及其可重複性都有影響。較大的電容值會改善誤 差的標準差,而該電路板實際適合的最大電容值為 100μF。

另外,還開發了一個客製的Python腳本,允許 直接控制激勵節點上的激勵頻率、直流和交流幅度, 並支援校準電阻調整。激勵訊號和接收訊號電路如 圖9所示。

將DUT的阻抗調低到10mΩ,會在更低頻率下顯 示同樣的誤差,如圖11所示。

www.eettaiwan.com | 2022年11月

TEST & MEASUREMENT