Page 15 - 腦機介面無回應?

P. 15

INDUSTRY TRENDS

13

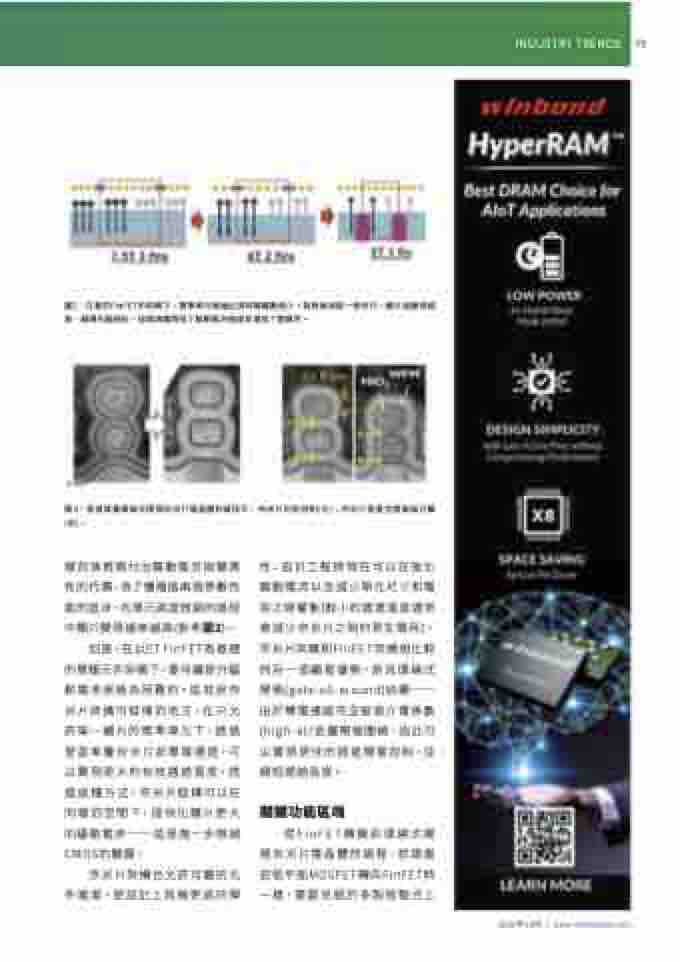

圖2:在基於FinFET的架構下,標準單元微縮必須伴隨鰭數減少。製程每演進一個世代,鰭片就變得越 高、越薄也越接近。這個演變降低了驅動電流強度並增加了變異性。

圖3:垂直堆疊環繞式閘極奈米片電晶體的最佳化:奈米片形狀控制(左);奈米片垂直空間縮減分離 (右)。

性:設計工程師現在可以在強化 驅動電流以及減少單元尺寸和電 容之間權衡(較小的通道寬度通常 會減少奈米片之間的寄生電容)。 奈米片架構和FinFET架構相比較 的另一個顯著優勢,是其環繞式 閘極(gate-all-around)結構── 由於導電通道完全被高介電係數 (high-k)/金屬閘極圍繞,因此可 以實現更佳的通道閘極控制,並 縮短通道長度。

從FinFET轉變到環繞式閘 極奈米片電晶體的過程,就跟當 初從平面MOSFET轉向FinFET時 一樣,需要克服許多製程整合上

樣的演進需付出驅動電流與變異 性的代價,為了彌補這兩個參數性 能的退步,在單元高度微縮的過程 中鰭片變得越來越高(參考圖2)。

但是,在以5T FinFET為基礎 的單鰭元件架構下,要持續提升驅 動電流是極為困難的。這就是奈 米片架構可發揮的地方,在只允 許單一鰭片的標準單元下,透過 垂直堆疊奈米片狀導電通道,可 以實現更大的有效通道寬度。透 過這種方式,奈米片結構可以在 同樣的空間下,提供比鰭片更大 的驅動電流──這是進一步微縮 CMOS的關鍵。

關鍵功能區塊

奈米片架構也允許可變的元 件寬度,使設計上具備更高的彈

2021年10月 | www.eettaiwan.com